- 您现在的位置:买卖IC网 > Sheet目录1203 > CORR-8BIT-XM-UT2 (Lattice Semiconductor Corporation)SITE LICENSE IP CORRELATOR XP

�� �

�

Lattice� Semiconductor�

�Correlator� IP� Core�

�block� can� be� a� maximum� of� 36� bits� wide,� therefore� if� the� number� of� correlator� cells� (MWIDTH)� is� not� greater� than�

�36,� only� one� column� of� EBR� memories� is� required� for� the� Coef?cient� Memories.� If� MWIDTH� >� 36,� then� multiple� col-�

�umns� will� be� con?gured.� As� in� the� case� of� the� Tap� Memories,� if� the� total� number� of� coef?cients� which� needs� to� be�

�stored� exceeds� one� row� of� EBR� memories,� then� multiple� rows� will� be� con?gured� in� a� stacked� arrangement� as�

�shown� in� Figure� 4.� For� MWIDTH� ≤� 36,� the� number� of� coef?cients� required� is� [NUM_TAP� *� NUM_COEF_SEQ].� If�

�this� number� is� less� than� 8192� then� only� one� EBR� is� needed� for� the� Coef?cient� Memory.�

�Unlike� the� Tap� Memories� which� are� written� with� new� user� data� under� the� control� of� the� state� machine,� the� Coef?-�

�cient� Memories� must� be� written� with� the� coef?cient� sequences� before� any� correlation� operations� can� be� done.� This�

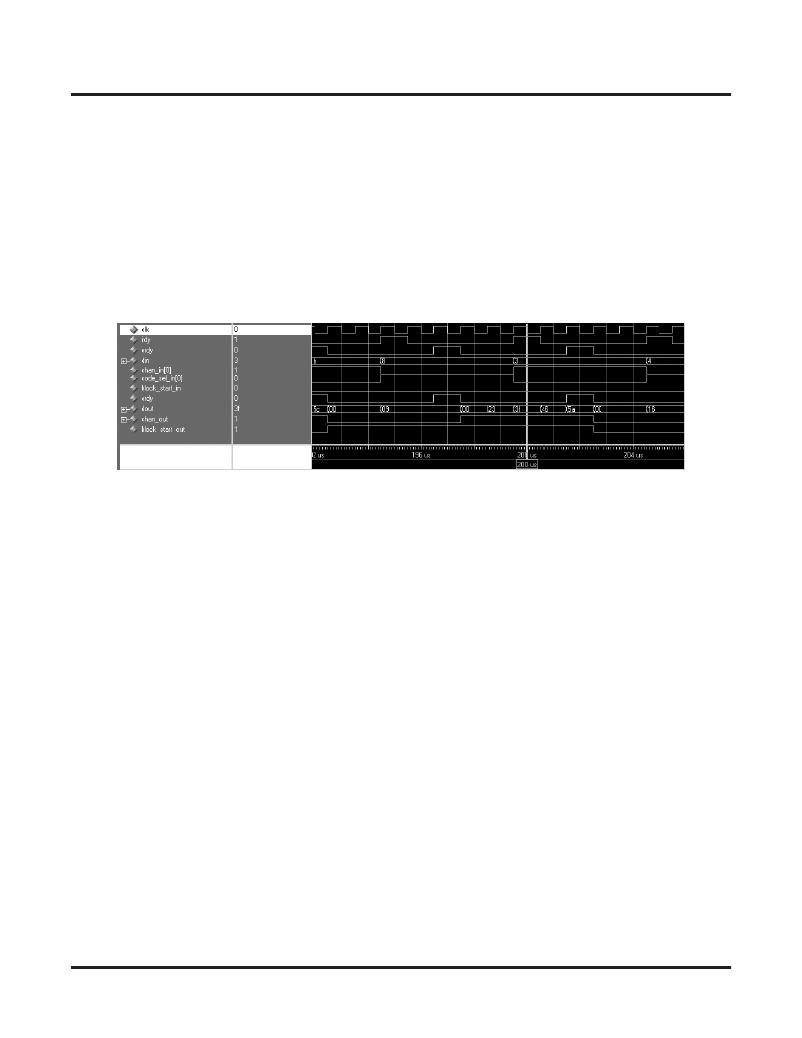

�is� done� via� the� Coef?cient� Memory� Con?guration� interface� shown� in� Figure� 5.� This� interface� consists� of� the� input�

�signals:� coeffaddr� ,� coeffwdat� ,� coeffwdat_im� ,� and� coeffwr� .� Figure� 6� shows� the� timing� for� this� interface� for�

�a� two-channel� design� with� MWIDTH=4,� NUM_TAP=16� and� NUM_COEF_SEQ=2.�

�Figure� 5.� Coef?cient� Memory� Con?guration� Interface� Timing�

�In� this� case,� the� Coef?cient� Memory� is� implemented� in� one� EBR� block.� Each� row� of� Coef?cient� Memory� is� required�

�to� store� MWIDTH=4� coef?cients,� so� each� write� to� the� memory� writes� four� bits.� Each� coef?cient� sequence� is�

�NUM_TAP=16� bits� long,� and� it� will� occupy� (NUM_TAP� /� MWIDTH)=� 4� rows� in� the� Coef?cient� Memory.� In� addition,� in�

�this� example� there� are� two� separate� coef?cient� sequences,� so� the� coef?cients� will� occupy� a� total� of� eight� rows� in�

�the� Coef?cient� Memory.�

�Writes� to� the� Coef?cient� Memory� are� enabled� by� asserting� the� coeffwr� input.� The� coeffaddr� input� selects� the�

�row� of� memory� to� be� written,� and� coeffwdat� (and� coeffwdat_im� for� complex� correlations)� is� set� to� the� desired�

�value.� This� is� a� very� simple� interface,� however� it� is� essential� to� make� sure� that� the� coef?cient� sequence� is� written� in�

�the� correct� order.� In� the� example� above,� the� ?rst� four� values� written� are� for� coef?cient� sequence� 0.� The� values� writ-�

�ten� are� 0xa6fc� (or� in� binary:� 1010� 0110� 1111� 1100)� with� the� LSB� being� the� ?rst� bit� in� the� correlation� sequence.� This�

�bit� will� be� multiplied� against� the� newest� data� value� received� by� the� Correlator.� The� MSB� in� this� string� will� be� multi-�

�plied� against� the� oldest� data� read� from� Tap� Memory.� This� is� explained� further� in� the� Correlator� Evaluation� Package�

�section� of� this� document.�

�The� second� coef?cient� sequence� written� into� the� Coef?cient� Memory� is� 0x0180,� and� is� written� into� rows� 7,� 6,� 5� and�

�4.� This� will� be� selected� as� coef?cient� sequence� 1� by� setting� the� code_sel_in� to� 1� when� a� data� value� is� input� to�

�the� Correlator.� Figure� 6� shows� how� the� coef?cient� values� from� this� example� would� appear� in� the� Coef?cient� Mem-�

�ory:�

�6�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

CP881

CONN BNC PLUG CRIMP RG-58

CP882

CONN BNC PLUG CRIMP RG-59,62

CPC2400E-EVAL

MODULE MODEM 2400BAUD EMBEDDEDED

相关代理商/技术参数

CORTEC VCI 101

制造商:CORTEC CORPORATION 功能描述:VCI EMITTER FOAM SMALL

CORTEC VCI 105

制造商:CORTEC CORPORATION 功能描述:VCI EMITTER TYVEK SM

CORTEC VCI 111

制造商:CORTEC CORPORATION 功能描述:VCI EMITTER TYVEK LGE

CO-SHINING EVB

制造商:Embest Info&Tech Co Ltd 功能描述:BOARD EVAL ARDUINO COMPATIBLE M051 制造商:Embest Info&Tech Co Ltd 功能描述:BOARD, EVAL, ARDUINO COMPATIBLE M051

COSIGRAPH 2

制造商:COSINUS 功能描述:SOFTWARE

COSP8436BK1

功能描述:机架和机柜配件 SOLID SIDE PANELS RoHS:否 制造商:Bivar 产品:Rack Accessories 面板空间: 颜色:Black

COST = 15.00 EACH FROM AS

制造商: 功能描述: 制造商:undefined 功能描述:

COTH-0150

制造商:TYAN 功能描述:CPU UPGRADE SET (INCLUDES POWER SUPPLY) FOR B4881 VX50 BAREB - Bulk